Displayport: Compliance And Signal Integrity Debugging

Explore a comprehensive overview of DisplayPort physical-layer compliance and signal integrity testing, focusing on both source device (transmitter) and cable evaluation. DisplayPort, a high-speed digital interface standard from VESA, now supports data rates up to 20 Gbps per lane for 8K displays and beyond. Ensuring interoperability at these speeds requires rigorous compliance testing per the DisplayPort Compliance Test Specification (CTS).

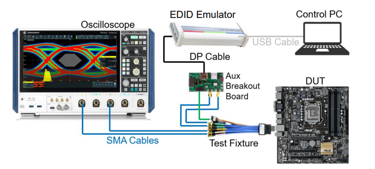

For source compliance, test points (TP2, TP3_EQ, TP3_CTLE) are defined for signal capture and analysis. Oscilloscope-based workflows, exemplified by Rohde & Schwarz’s ScopeSuite, allow automated evaluation of voltage swing, eye diagrams, and jitter at these points, rapidly identifying compliance failures or margin concerns. Equalization (CTLE, DFE) and jitter decomposition tools facilitate in-depth debugging to address issues such as inter-symbol interference and timing instability.

Cable quality is equally crucial and assessed using Vector Network Analyzers (VNAs) to measure S-parameters (insertion loss, return loss, crosstalk). Mixed-mode S-parameter analysis accurately reflects real-world differential signaling. Additional tools, like Time Domain Reflectometry (TDR), localize impedance discontinuities, while simulated eye diagrams using measured data reveal potential link limitations.

The document highlights necessary instrumentation for both test types and outlines calibration, measurement, and debug procedures that align with VESA and industry requirements. Ultimately, Rohde & Schwarz’s automated and manual tools offer a robust workflow for verifying compliance, diagnosing failures, and ensuring reliable DisplayPort performance across products and generations.

Get unlimited access to:

Enter your credentials below to log in. Not yet a member of RF Globalnet? Subscribe today.