JESD204B Clock Generator: AD9528

Source: Analog Devices

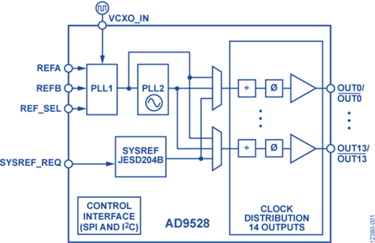

The AD9528 is a two-stage PLL with an integrated JESD204B SYSREF generator for multiple device synchronization. The AD9528 can also be used as a dual input flexible buffer to distribute 14 device clock and/or SYSREF signals.

Product Applications Include:

- High performance wireless transceivers

- LTE and multicarrier GSM base stations

- Wireless and broadband infrastructure

- Medical instrumentation

- Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs; supports JESD204B

- Low jitter, low phase noise clock distribution

- ATE and high performance instrumentation

Additional Product Features Include:

- 14 outputs configurable for HSTL or LVDS

- Maximum output frequency

- Dependent on the voltage controlled crystal oscillator

- Dedicated 8-bit dividers on each output

- Typical output to output skew: 20 ps

- Duty cycle correction for odd divider settings

- Output 12 and Output 13, VCXO output at power-up

- Absolute output jitter: <160 fs at 122.88 MHz, 12 kHz to 20 MHz integration range

- Digital frequency lock detect

- SPI- and I2C-compatible serial control port

- Dual PLL architecture

For more information on this product, download the available datasheet.