AWR Collaborates With Jazz Semiconductor On 5.8 GHz RFIC SiGe BiCMOS Design

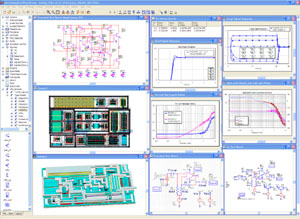

El Segundo, CA -- Applied Wave Research, Inc. announced that the company's Analog Office design suite,

a software product developed specifically for analog and radio-frequency

integrated circuit (RFIC) design, has recently been used by a major Japanese

electronics manufacturer to successfully design a 5.8GHz RFIC in an advanced

silicon germanium (SiGe) bipolar complimentary metal oxide semiconductor

(BiCMOS) process from Jazz Semiconductor.

El Segundo, CA -- Applied Wave Research, Inc. announced that the company's Analog Office design suite,

a software product developed specifically for analog and radio-frequency

integrated circuit (RFIC) design, has recently been used by a major Japanese

electronics manufacturer to successfully design a 5.8GHz RFIC in an advanced

silicon germanium (SiGe) bipolar complimentary metal oxide semiconductor

(BiCMOS) process from Jazz Semiconductor. The RF receiver, according to the company, is the first complete silicon-based RFIC successfully designed and taped out using the entire Analog Office design flow from schematic capture, through simulation, analysis, layout, extraction and complete design rule check (DRC), and layout versus schematic (LVS) verification. The design commenced in May 2005 and was taped out to Jazz Semiconductor's Newport Beach wafer foundry in August 2005. The resulting silicon, delivered and tested in October 2005.

"This first-time-success in a complex RFIC at 5.8GHz validates the use of AWR's streamlined design flow along with Jazz Semiconductor's silicon-accurate RF models for the fast realization of complex RF products," said Marco Racanelli, vice president of engineering at Jazz Semiconductor. "Our customer indicated that the Analog Office RFIC design system, with its unified data model and powerful design environment, enabled its engineers to design the entire chip in one integrated platform and helped them achieve first-pass success in silicon. Jazz is pleased to continue working with AWR in support of our mutual customers in order to enable rapid time-to-market for the introduction of future innovative products."

"We are extremely pleased that the Analog Office product fully met the customer's expectations, streamlined the silicon design process, and helped the company deliver fully-functional silicon in such record time," said James Spoto, AWR president and CEO. "We are looking forward to working with this customer and other mutual Jazz customers on future silicon RFIC designs."

SOURCE: Cadence Design Systems, Inc.